The layout of a design must be in accordance with a set of predefined technology rules given by the foundry for manufacturability. After completion of the layout and its physical connection, an automatic program will check each and every polygon in the design against these design rules and report any violations. This whole process is called Design Rule Checking (DRC). There are many design rules at different technology nodes, a few of which are mentioned below.

Types of DRCs:

- Minimum width and spacing for metal

- Minimum width and spacing for via

- Fat wire Via keep out Enclosure

- End of Line spacing

- Minimum area

- Over Max stack level

- Wide metal jog

- Misaligned Via wire

- Different net spacing

- Special notch spacing

- Shorts violation

- Different net Via cut spacing

- Less than min edge length

Here are some of the practical problems and their solution for different types of DRCs and their solutions.

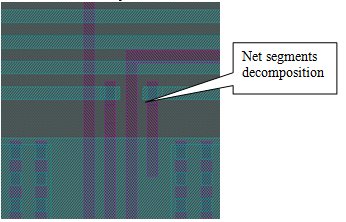

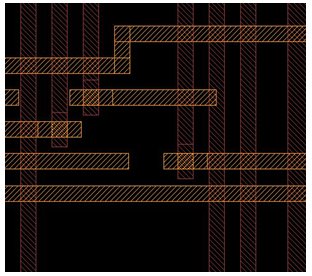

CASE A: Shorts violation

Description: In short violation, two or more different net segments of the same layer were crossing each other. Here is a practical problem of two different nets in same metal layer crossing to each other as seen in the following pic.

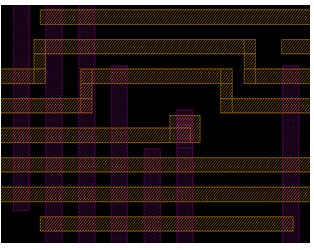

Solution:

To fix this type of short violation, different net segments on same layer has to be placed away so that they will not cross each other. In this case, net adjusted net will not cross each other and also meet the spacing requirement in the same layer.

CASE B: Different Spacing violation

Description : In some cases, the via enclosure is quite large compared to metal width due to large via enclosure. Thee other long net passing each other and dropped in via will create a different spacing violation.

Solution:

To fix this type of spacing violation, the net needs to be placed away from the via, or different size vias need to be inserted so it will meet the same net spacing requirement. In above case, routing taken in reverse U shape will meet the spacing requirements as below.

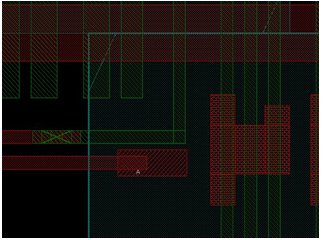

CASE C: Same layer spacing with net and cell geometry blockage

Description: In this case, there is same layer spacing with the cell blockage and via enclosure

Highlighted in pic using white marker. Same net spacing in red color.

Solution:

In this case, to fix violation, the net is routed in non-preferred direction in green color inserted via so spacing is increased between cell blockage and a net.

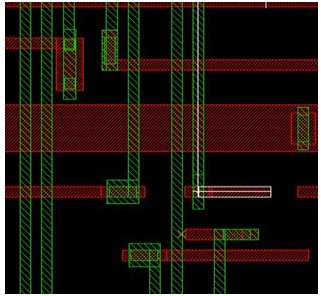

CASE D: Minimum area requirement

Description: There is a minimum area requirement for every segment in a layout.

Solution:

To meet this minimum area requirement, we need to increase the area of the segment that will not violate the other design rule (spacing, short). For this case I have increase the area where I was getting the violation shown below.

CASE E: VIA Misalignment

Description: This type violation pops up when two different layer of same logical net connected by inserting the VIA. If inserted via is not aligning with the metal crossing we are seeing the VIA misalignment.

Solution:

Proper VIA instance need to insert so the VIA enclosure align layer in its direction properly and if needed we need to stretch the net and insert the VIA.

After fixing the all DRC again we need to verify drc with different tool Caliber,Quartz before releasing to foundary because while fixing the drc there may be a chances of populating the new DRC violation.