How to add ndms in ref_libs

Open

block.tcl file

Report_ref_libs

information dump in a new tcl file

Now

go to icc2shell

set_ref_libs

-add missed ndm file---> from block.tcl

file

set_ref_libs

-rebind

link_block

-force

report_ref_libs

save_block

save_lib

How to resolve upf error ?

commit_upf

save_block

save_lib

How to move ESD cell with origin coordinates ?

move_objects

[get_selection ] -to {7486.0965 3288.0000}

How to select all the cells which have net name

VDD_1V2_IO ?

change_selection

[get_cells -of_objects [get_net VDD_1V2_IO]]

Cmd for to check shorts

check_lvs -max_error 0

-checks short----->for

to check shorts

How to add buffers

add_buffer

-lib_cell ec0cbf000an1n20x5 -new_cell_names 01122019_cell -new_net_names

01122019_net [get_pins lgcio_pch/giolgcpchtop/lgciopchdig/chaitanya_fix_3/clk]

For to check open nets for a specific net

check_lvs -checks

open -nets {biss_bg_vref_out} -open_reporting detailed------>for to check

opens of a specific net

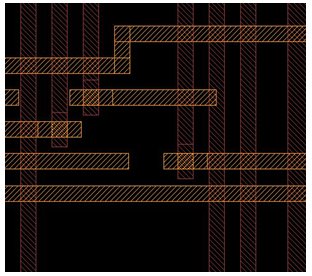

How to load bumps

read_def -add_def_only_objects {cells nets ports} def file path

How to

prepare Empty db

change_selection [get_cells *BUMP*]

remove_objects [get_selection ]

change_selection [get_shapes -of_objects

-filter "layer_name==AP"]

change_selection [get_shapes -filter "layer_name==AP"]

change_selection [get_shapes -filter "layer_name==M11"]

change_selection [get_vias -filter "upper_layer_name==M11 ||

upper_layer_name==AP "]

remove_objects [get_selection ]

How to get def file?

Select whatever u need in tool then use below command

write_def -objects [get_selection] filename.def

How to load def?

First create empty

db

Then use below

command

read_def

-add_def_only_objects {cells nets ports} def path

To create cell

create_cell inst_TMS_SWDIO */io_sndwire_fs_1v2_1v8_n1

move_objects [get_cell inst_1V8_SUP1V8_1 ] -to {4250.0000

0.0000}

To get cells

change_selection [get_cells -of_objects [get_nets VDD_DIG_BIS]]

sizeof_collection

[get_cells]

To select all cells

lsort -u [get_attribute [get_selection ] object_class ]

Remove_cells [get_selection]

getting particular pins

get_pins par_opio/*xx*

connecting and disconnecting nets

Connect_net -net name pin name

Disconnect_net -net name pin name

cs [gp -of [gn vccvdd2_rpll_hv]]

get_nets -of_objects [gs]

How to remove terminals?

change_selection

[get_terminals *]

remove_objects

[get_selection]

How to take

routes with tcl

Off terminal,ports,cells

First select nets

Give get selection

Then take that net names and paste in this cmnd

on braces

1.change_selection [get_shapes -of_objects

[get_nets netname]] then u will get that

net nets shapes

2.change_selection [get_viass -of_objects [get_nets netname

]] -add

3. lsort -u

[get_attribute [get_selection ] object_class ]

4.write_routes -objects [get_selection ]

-output filename

To know width of the layer

ga [get_layer m9] min_width

For to remove cells from design

Remove_cellls [get_selection]

For to select that net shapes in specific Layer

change_selection

[get_shapes -of_objects [get_net VDD_1V2_IO] -filter

"layer_name==M10"]

For

to know cell count

sizeof_collection

[get_selection]

How to drop Vias in a perticular place by using

commands.

By using bound option

first create bound on that area

Next by using this

command u can create vias for specific nets by selecting that bound

get_attribute

[get_selection ] bbox

How to remove vias from a particular location

Here

I am removing m10 vias

First

draw bound on the area where u required.

Next

use below commands

get_attribute

[get_selection ] bbox

change_selection

[get_vias -within {give bbox coordinates}

-filter "upper_layer_name==M11 || upper_layer_name==M10"]